- 您现在的位置:买卖IC网 > Sheet目录3889 > PIC16F873T-04E/SO (Microchip Technology)IC MCU FLASH 4KX14 EE 28SOIC

PIC16F87X

DS30292C-page 114

2001 Microchip Technology Inc.

11.1

A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy,

the charge holding capacitor (CHOLD) must be allowed

to fully charge to the input channel voltage level. The

analog input model is shown in Figure 11-2. The source

impedance (RS) and the internal sampling switch (RSS)

impedance directly affect the time required to charge

the capacitor CHOLD. The sampling switch (RSS)

impedance varies over the device voltage (VDD), see

Figure 11-2. The maximum recommended imped-

ance for analog sources is 10 k

. As the impedance

is decreased, the acquisition time may be decreased.

After the analog input channel is selected (changed),

this acquisition must be done before the conversion

can be started.

To

calculate

the

minimum

acquisition

time,

Equation 11-1 may be used. This equation assumes

that 1/2 LSb error is used (1024 steps for the A/D). The

1/2 LSb error is the maximum error allowed for the A/D

to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see

the

PICmicro

Mid-Range

Reference

Manual

(DS33023).

EQUATION 11-1:

ACQUISITION TIME

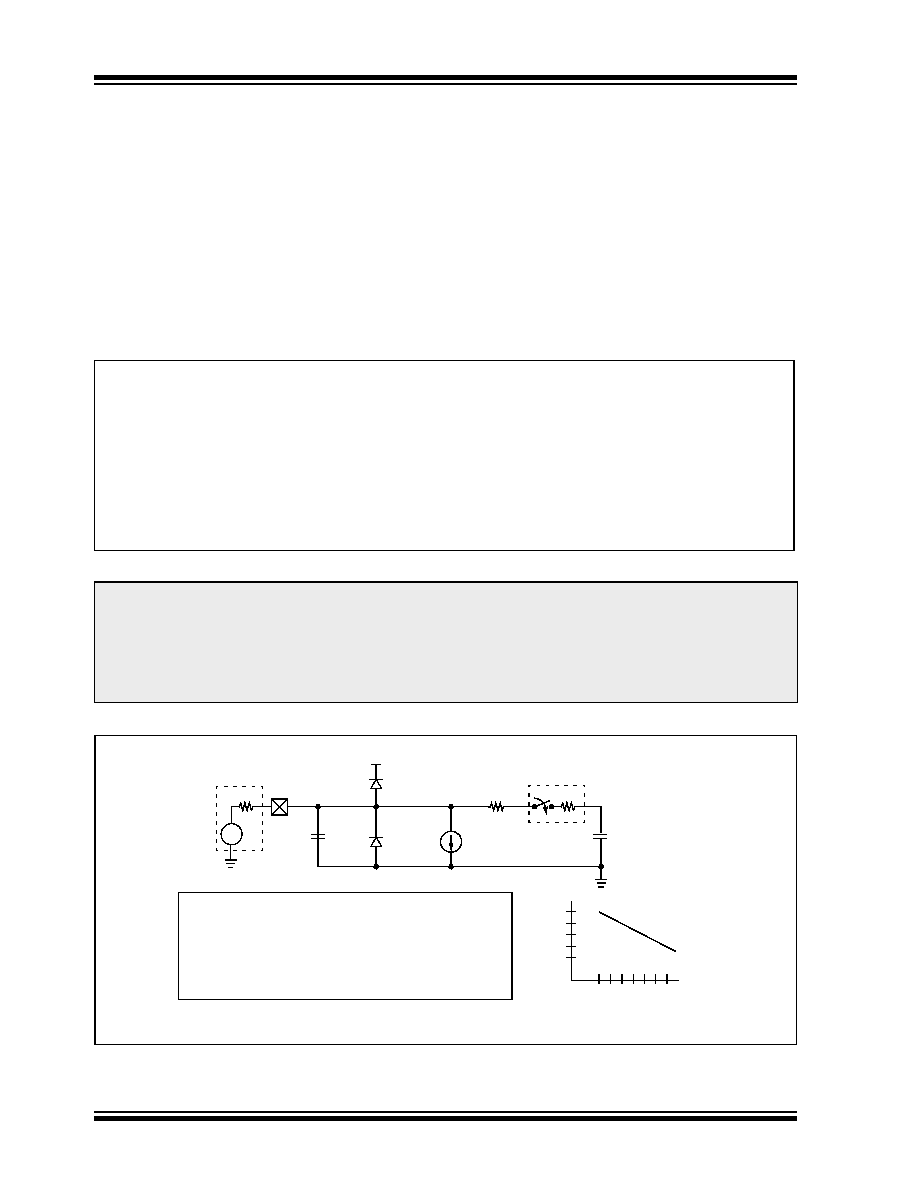

FIGURE 11-2:

ANALOG INPUT MODEL

TACQ

TC

TACQ

=

Amplifier Settling Time +

Hold Capacitor Charging Time +

Temperature Coefficient

TAMP + TC + TCOFF

2

s + TC + [(Temperature -25°C)(0.05s/°C)]

CHOLD (RIC + RSS + RS) In(1/2047)

- 120pF (1k

+ 7k + 10k) In(0.0004885)

16.47

s

2

s + 16.47s + [(50°C -25°C)(0.05s/°C)

19.72

s

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

3: The maximum recommended impedance for analog sources is 10 k

. This is required to meet the pin leak-

age specification.

4: After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again.

During this time, the holding capacitor is not connected to the selected A/D input channel.

CPIN

VA

RS

ANx

5 pF

VDD

VT = 0.6V

I LEAKAGE

RIC

≤ 1k

Sampling

Switch

SS RSS

CHOLD

= DAC capacitance

VSS

6V

Sampling Switch

5V

4V

3V

2V

567 8 9 10 11

(k

)

VDD

= 120 pF

± 500 nA

Legend

CPIN

VT

I LEAKAGE

RIC

SS

CHOLD

= input capacitance

= threshold voltage

= leakage current at the pin due to

= interconnect resistance

= sampling switch

= sample/hold capacitance (from DAC)

various junctions

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16F877T-10E/PT

IC MCU FLASH 8KX14 EE 44TQFP

22-15-3053

CONN FFC/FPC 5POS .100 RT ANG

PIC16C58BT-40/SS

IC MCU OTP 2KX12 20SSOP

PIC16C57CT-40/SO

IC MCU OTP 2KX12 28SOIC

PIC16C55AT-40/SO

IC MCU OTP 512X12 28SOIC

PIC16C56AT-40/SO

IC MCU OTP 1KX12 18SOIC

PIC16C57CT-40/SS

IC MCU OTP 2KX12 28SSOP

22-02-3053

CONN FFC/FPC 5POS .100 VERTICAL

相关代理商/技术参数

PIC16F873T-04I/SO

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F873T-10E/SO

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F873T-20/SO

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F873T-20I/SO

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F874-04/L

功能描述:8位微控制器 -MCU 7KB 192 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F874-04/L

制造商:Microchip Technology Inc 功能描述:8BIT FLASH MCU SMD 16F874 PLCC44

PIC16F87404/P

制造商:Microchip Technology Inc 功能描述:MICROCONTROLLER IC

PIC16F874-04/P

功能描述:8位微控制器 -MCU 7KB 192 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT